# ウェイクアップ型無線通信のためのグループ指定可能 ID マッチング機構の実装

Implementation of a Group-Based ID Matching Mechanism for Wake-up Wireless Communication

石田 繁巳 瀧口 貴啓 猿渡 俊介 南 正輝 森川 博之

Takahiro Takiguchi Shunsuke Saruwatari Masateru Minami Shigemi Ishida Hiroyuki Morikawa

東京大学先端科学技術研究センター / Research Center for Advanced Science and Technology, The University of Tokyo

### はじめに

無線通信モジュールは受信待機時にも受信時と同程度の電力を消費する ため、受信待機時間の長いアプリケーションでは受信待機電力を削減することが重要である。筆者らは、ウェイクアップ型の無線通信を行うことで受信 待機電力を削減するウェイクアップ型無線通信システムの実現を目指してい 本稿では,グループ指定ウェイクアップを実現するための ID マッチン グ回路の  $0.18 \, \mu \text{m}$  CMOS チップ実装について述べる.

## ウェイクアップ型無線通信システム

ウェイクアップ型無線通信システムは,低消費電力な無線通信モジュールを用いて受信待機を行うことで受信待機電力を削減する無線通信システ んである。ウェイクアップ型無線通信システムはデータ通信モジューウェイクアップでは、データンのモジュールで構成される。データン ウェイクアップモジュールの 2 つのモジュールで構成される。データ通信モジュールは Wi-Fi,Bluetooth,ZigBee などの汎用無線通信モジュールである。ウェイクアップモジュールは電波検出回路と ID マッチング回路から構成される。電波検出回路は受信待機時に動作する唯一の回路であり,ウェイクアップチャネルの電波検出を行う。数十  $\mu$ W 程度の消費電力で動作し,電波を検出すると ID マッチング回路をウェイクアップさせる。ID マッチング回路がウェイクアップするとウェイクアップパケットを受信し,ウェイクアップパケットに含まれる ID に基づいて自端末がウェイクアップ対象であるかどうかを判定して,データ通信モジュールをウェイクアップさせる。ID マッチング回路を用いることで不要なウェイクアップを削減し,受信待機電力を効果的に削減することが可能となる 機電力を効果的に削減することが可能となる

## ウェイクアップモジュールディジタル回路の設計

ウェイクアップ型無線通信システムをすれちがい通信に適用することを 考え,筆者らはブルームフィルタを用いたグループ指定可能な ID マッチングを提案している [1]. ウェイクアップ型無線通信システムの実現に向けて,ウェイクアップパケットを受信して ID マッチングを行う回路の設計を

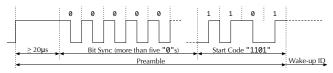

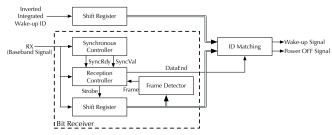

行った. 図 1 に本実装で用いるウェイクアップパケットのフレーム構成を示す. ウェイクアップパケットはプリアンブルとウェイクアップ ID から構成され, マンチェスタ符号を用いて符号化する. 電波検出回路で電波を検出しやすくするため, プリアンブルの先頭で無変調の搬送波を送信する. 無変調信号の後にはビット同期用信号と, ウェイクアップ ID の開始位置を示すスタートコードを送信する. プリアンブルの後には固定長のウェイクアップ ID を送信する. 本実装では, 無変調信号は 20 μs 以上とし, ビット同期用信号として 5 ビット以上の 0 を, スタートコードとして 1101 という 4 ビットの値を用いる. また, ウェイクアップ ID 長は 128 ビットとする. 図 2 に設計したウェイクアップ ID 長は 128 ビットとする. 図 2 に設計したウェイクアップモジュールのディジタル回路を示す. ウェイクアップモジュールのディジタル回路を示す. ウェイクアップモジュタ, 同期制御回路, 受信制御回路, 受信 ID 用シフトレジスタ, フレーム検出回路, ID マッチング回路という 6 つのブロックから構成され

シフトレジスタ,同期制御回路,受信制御回路,受信 ID 用シフトレジスタ, フレーム検出回路,ID マッチング回路という 6 つのブロックから構成され る. 設計には Verilog HDL を用いた

る. 設計には Verilog HDL を用いた.

ウェイクアップモジュールのディジタル回路は, アナログ回路である電波検出回路の出力によってウェイクアップし, 以下のような動作を行う. 統合ウェイクアップ ID 登録用シフトレジスタには, ID マッチングに先立ってビット反転した統合ウェイクアップ ID を格納する. ディジタル回路がウェイクアップすると, 同期制御回路がウェイクアップパケットプリアンブルのビット同期用信号を用いてビット同期を行う. ビット同期が完了すると, 1 ビットの周期を表す SyncVal と同期完了信号 SyncRdy を出力する。受信制 御回路は SyncRdy の出力により動作を開始し、SyncVal とウェイクアップパパケットの立ち上がりまたは立ち下がりエッジを用いて、ウェイクアップパ ケットの各ビットに対するストローブ信号 Strobe を出力する.受信 ID 用 シフトレジスタは,Strobe によってウェイクアップパケットを 1 ビットす 受信 ID 用 つ格納する。フレーム験出回路は、シフトレジスタに格納されているウェイクアップパケットを監視し、スタートコードを検出するとフレームスタート ラティア・アットで監視し、ペクートコートを映出するとフレームペップド 信号 Frame を出力する。Frame によって受信制御回路は受信ビット数のカ ウントを開始し、ウェイクアップ ID 長のビット数を受信すると受信完了信 号 DataEnd を出力する。ID マッチング回路は DataEnd の出力によって ID マッチングを開始し、結果に応じてウェイクアップ信号またはパワー OFF 信号を出力する.

## ウェイクアップモジュールディジタル回路の実装

回路レベルのシミュレーション結果と実際に得られるチップの性能を比較 するため、ウェイクアップモジュールのディジタル回路を  $0.18\,\mu\mathrm{m}$  トリプ

図1 ウェイクアップパケットのフレーム構成

図 2 ウェイクアップモジュールのディジタル回路

ルウェル 1-Poly 5-Metal CMOS プロセスを用いて実装した。電源電圧は  $0.18\,\mu\mathrm{m}$  プロセスで広く使用されている  $1.8\,\mathrm{V}$  である.Verilog HDL を用いて設計したディジタル回路を,Synopsys 社の Design Compiler [2] を用 いて論理合成し、Synopsys 社の Astro [3] を用いて配置配線を行ってチップレイアウトを得た。 ID マッチングは、受信機に登録されている複数の ID の中に受信したウェ

ID メッケンクは、文店域に豆塚されている懐教のID の中に文信したりエイクアップ ID と一致する ID があるかどうかの確認を行う。本実装では、ブルームフィルタを用いて複数の ID を 1 つのビット列に変換して受信機に登録するが、同様の ID マッチングは受信機内に複数のレジスタを用意し、複数の ID を保持することでも実現できる。ブルームフィルタを用いる場合と複数レジスタを用いる場合を比較するため、複数レジスタ方式の ID マッチング回路についても実践を行った。目体的には、ID を投始することです。 チング回路についても実装を行った。具体的には、ID を格納するレジスタ数が1個,5個の回路をそれぞれ実装した。入出力に使用可能なピン数が限られているため入出力ピンは各 ID マッチング回路で共通のものを使うこと し、選択した ID マッチング回路を入出力ピンに接続するための入出力制

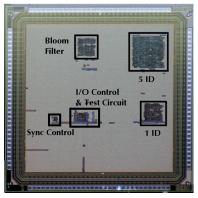

御回路を実装した。また、デバッグ用のテスト回路の実装も行った。 図 3 に試作したディジタル回路のチップ写真を示す。チップサイズは  $2.5\,\mathrm{mm} \times 2.5\,\mathrm{mm}$  である。各 ID マッチング回路は、統合ウェイクアップ ID(または複数 ID)登録用シフトレジスタ,受信制御回路,受信 ID 用シフトレジスタ,フレーム検出回路も含んでいる。各回路ブロックの回路面積 は、同期制御回路が  $65\,\mu\mathrm{m} \times 65\,\mu\mathrm{m}$ 、ブルームフィルタを用いる ID マッチング回路が  $255\,\mu\mathrm{m} \times 235\,\mu\mathrm{m}$ 、1 個、5 個の ID と比較を行う ID マッチン グ回路がそれぞれ  $255\,\mu\mathrm{m} \times 235\,\mu\mathrm{m}$ ,  $430\,\mu\mathrm{m} \times 430\,\mu\mathrm{m}$  である.

本稿では、ウェイクアップ型の無線通信実現に向けたウェイクアップモ ジュールディジタル回路の CMOS チップ実装について述べた。現在、試作 したチップの消費電力評価を行っている.

本研究は、戦略的創造研究推進事業(CREST)の支援,及び東京大学大規模集積システム設計教育研究センターを通し、シノプシス株式会社,ケイデンス株式会社,メンター株式会社の協力で行われたものである。

## 参考文献

- S. Ishida *et al.*: "Evaluation of a wake-up wireless module with bloom-filter-based ID matching", APSITT2010.

- Synopsys: "Design Compiler Ultra", http://www.synopsys.com/ Tools/Implementation/RTLSynthesis/Pages/DCUltra.aspx.

- [3] Synopsys: "Astro".

図3 試作したディジタル回路のチップ写真